LA1 (Modul 2)

Rangkaian dalam percobaan pertama menggunakan JK flip-flop dengan PRESET dan CLEAR, serta D flip-flop yang juga memiliki PRESET dan CLEAR. Inputnya adalah saklar yang terdiri dari 7 switch bernama B0 hingga B6, yang terhubung ke VCC. B0 dihubungkan ke CLEAR pada kedua flip-flop, sedangkan B1 terhubung ke PRESET pada kedua flip-flop. B2 menghubungkan J pada JK flip-flop, B3 menghubungkan CLOCK (aktif pada saat fall time) pada JK flip-flop, B4 terhubung ke K pada JK flip-flop, B5 terhubung ke D pada D flip-flop, dan B6 menghubungkan CLOCK (aktif pada saat rise time) pada D flip-flop. Masing-masing flip-flop memiliki dua output, yaitu Q dan Q’, yang semuanya dihubungkan ke logic probe untuk mendeteksi adanya sinyal keluaran.

Prinsip kerja rangkaian ini adalah dengan mengubah status dari 7 switch untuk memvariasikan input flip-flop. Sesuai dengan tabel kebenaran, keluaran dari setiap flip-flop akan bervariasi berdasarkan kombinasi input.

Sebagai contoh, pada percobaan pertama dengan variasi pertama, jika B0 (CLEAR) = 0, B1 (PRESET) = 1, B2 (J) tidak berpengaruh, B3 (CLOCK) tidak berpengaruh, B4 (K) tidak berpengaruh, B5 (D) tidak berpengaruh, dan B6 (CLOCK) tidak berpengaruh, maka output dari JK flip-flop adalah Q = 0 dan Q' = 1, serta output dari D flip-flop adalah Q = 0 dan Q' = 1. Ini terjadi karena input PRESET dan CLEAR pada flip-flop RS tidak sama, sehingga RS flip-flop yang aktif, sementara D flip-flop dan JK flip-flop tidak aktif. Output yang dihasilkan sesuai dengan tabel kebenaran RS flip-flop, yaitu Q = 0 dan Q' = 1.

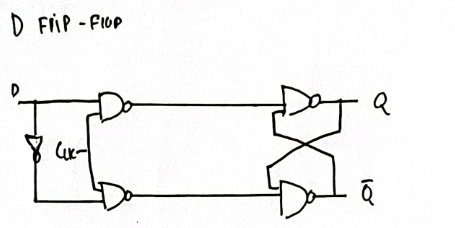

Rangkaian dasar D FF

- Pada nomor 1, saat B6 dan B5 = don't care, Maka menghasilkan Q = 0 dan Q̅ = 1, sesuai dengan percobaan

Pada nomor 2, saat B6 dan B5 = don't care Maka outputnya 1 dan 0

Pada nomor 3, path saat B6 dan B5 = don't care,Maka outputnya Q = 1 dan Q̅ = 1,

Nomor 1 sampai 3 terjadi berubah ubah karena Input B6, B5, B1, B2, B3, B4, dan B5 berpengaruh Pada D FF

Pada nomor 4, saat B6 = 0 mengikuti input sebelumnya dan B5 = 0, maka outputnya Q̅ = 0 dan Q̅ = 1

Pada nomor 5, saat B6 = mengikuti input sebelumnya, B5 = 1 maka outputnya Q = 0 dan Q̅ = 1

Pada nomor 6, saat B6 = 0 dan B5 = don't care maka outputnya Q = 0 dan Q̅ = 0

Pada nomor 7, saat B6 = DIPUTUS, dan B5= DIPUTUS maka outputnya Q = = dan Q̅ = - menunjukkan output sebelumnya

Komentar

Posting Komentar