Modul 1 (Percobaan 1 Kondisi 10)

(Percobaan 1 Kondisi 10)

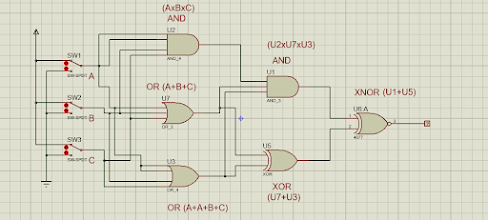

Buatlah sebuah rangkaian lengkap yang memuat 2 gerbang AND dengan 3 input dan 4 input, kemudian gerbang OR dengan 2 dan 4 input,kemudian 1 gerbang XOR dan 2 gerbang XNOR. Dan output akhir rangkaian keseluruhannya ditunjukkan dengan LED atau LOGIC PROBE. Dimana input awal berupa 3 saklar SPDT.

2. Gambar Rangkaian Simulasi[Kembali]

Input (Saklar SPDT): Ada 3 saklar SPDT (A, B, C), yang masing-masing bisa dihubungkan ke VCC (logika '1') atau ke ground (logika '0'). Kombinasi dari ketiga saklar ini akan menghasilkan 8 variasi data input (kombinasi dari A, B, dan C).

Gerbang AND:

And adalah A * B * C, jika salah satu kali bernilai 0 maka kaki outputnya bernilai 0Gerbang OR:

Or adalah A+B+C, selama salah satu kakinya bernilai 1 maka tetap 1Gerbang XOR:

jika dua dua nya 1,maka outputnya 0, jika dua duanya 0 maka 0, jika salah satu nya 1 maka 1 (jika kaki nya ganjil maka outputnya 1)Gerbang XNOR: jika jumlah kaki berjumlah genap, maka inputnya berlogika 0, jika inputnya bernilai ganjil maka inputnya bernilai 1

Output Logic Probe: sesuai dengan penjelasan XNOR, kita dapatkan outputnya, karena dalam percobaan nilai xnor nya adalah 1 dan 0 maka outputnya 0

Komentar

Posting Komentar